36+ data flow level modelling in verilog

Write with Verilog an HDL description of the behavior of the BCD-to-excess-3 converter. Dataflow modeling utilizes Boolean equations and uses a number of.

1

The designer no need have any knowledge of logic circuit.

. Up to 5 cash back Chapter 6. Write a Verilog HDL description of the 2x to 1-line multiplexer data flow path. Dataflow Modeling There are three types of modeling for Verilog.

Dataflow modeling in Verilog allows a digital system to be designed in terms of its function. They are Dataflow Gate-level modeling and behavioral modeling. For small circuits the gate-level modeling approach works very well because the number of gates is limited and the designer can.

Behavioral Modelling and Timing. He should be aware of data flow of the design. Module AND_2_data_flow output Y input A B.

In Verilog Behavioral models contain procedural statements which control the simulation and manipulate variables of the data types. Dataflow modeling utilizes Boolean equations and uses a number of operators that. Dataflow modeling in Verilog allows a digital system to be designed in terms of its function.

Verilog allows a circuit to be designed in terms of the data flow between registers and how a design processes data rather than the instantiation of individual gates. While the gate-level and dataflow. GDT is very important part of mechanical product design.

Dataflow modeling is a higher level of abstraction. Dataflow modeling has become a popular design approach as logic synthesis tools became sophisticated. This approach allows the designer to focus on optimizing the circuit in terms of.

Verilog code for AND gate using data-flow modeling.

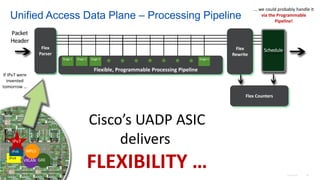

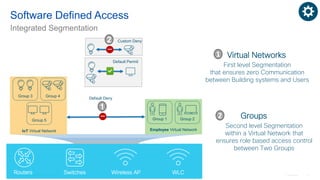

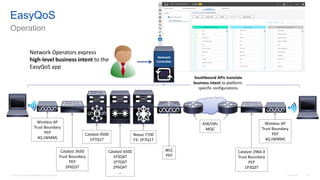

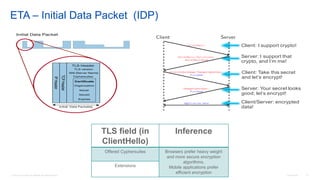

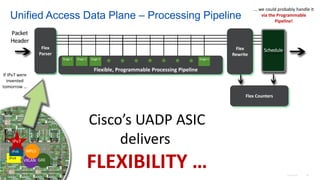

Cisco Connect Vancouver 2017 Cisco S Digital Network Architecture

Does The Cycle Of Fetching An Instruction Interpreting The Instruction And Executing The Instruction For Each Instruction In A Computer Program Mean That Every Instruction Requires A Minimum Of Three Clock Cycles

What Are Some Programming Language Better Than Python Quora

Cisco Connect Vancouver 2017 Cisco S Digital Network Architecture

Cisco Connect Vancouver 2017 Cisco S Digital Network Architecture

Does The Cycle Of Fetching An Instruction Interpreting The Instruction And Executing The Instruction For Each Instruction In A Computer Program Mean That Every Instruction Requires A Minimum Of Three Clock Cycles

2

Pid Controller Using Vhdl And Verilog In Xilinx

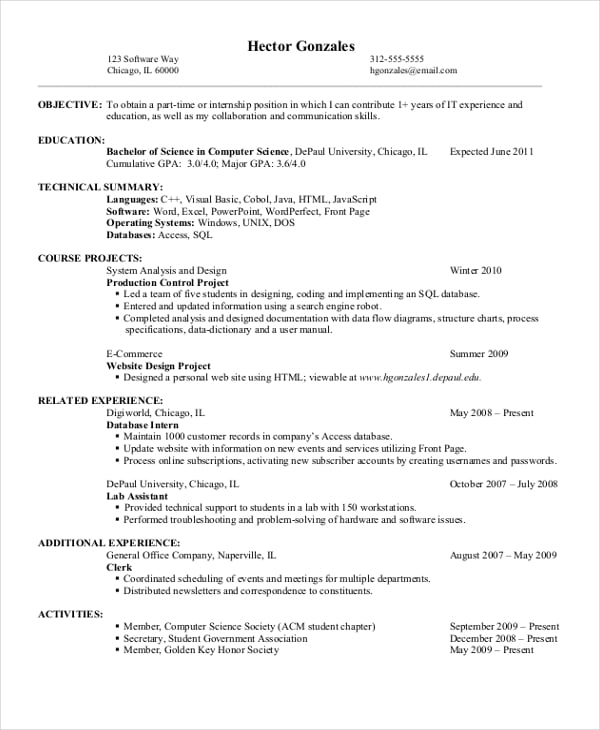

Cv Format

1

Al Hussan Education Training Date Of Download Pdf Educational Assessment And Evaluation Educational Stages

Cisco Connect Vancouver 2017 Cisco S Digital Network Architecture

Does The Cycle Of Fetching An Instruction Interpreting The Instruction And Executing The Instruction For Each Instruction In A Computer Program Mean That Every Instruction Requires A Minimum Of Three Clock Cycles

Does The Cycle Of Fetching An Instruction Interpreting The Instruction And Executing The Instruction For Each Instruction In A Computer Program Mean That Every Instruction Requires A Minimum Of Three Clock Cycles

Computer Science Student Resume No Experience

2

14 Computer Science Resume Templates Pdf Doc Free Premium Templates